Synchronous counter-In this all the flip-flops work in sync with clock pulse as well as each other. It got its name because the clock pulse ripples through the circuit. Dt

The initial content of the 4 bit Serial IN Parallel Out shift register is shown in Figure is 1100. endstream

endobj

23 0 obj

<>stream

An n-MOD ripple counter contains n number of flip-flops and the circuit can count up to 2n values before it resets itself to the initial value. This traffic light has to be implemented using a finite state machine (FSM). hTOO |9j{gaZI,)=Xx =clF^wa~!p:U`]O* On#N<4

9GZ+q uc\WTpBA`p`x5 TwFRnDh2tTA*bDu+3UPH(9m{9I^[ pr

endstream

endobj

24 0 obj

<>stream

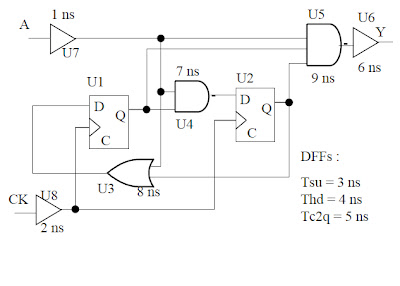

Hence themaximum clock frequency is 6.25 MHz. endstream

endobj

22 0 obj

<>stream

For a 16-bit signed integer, SLC 500 counters can count within the range of: A traffic signal cycles from GREEN to YELLOW, YELLOW to RED and RED to GREEN. Ltd.: All rights reserved, Each flip-flop in a 4-bit ripple counter introduces a maximum delay of 40 n sec. hb```f``2f`a`lac@ >r,`haPPxz^(f`fefe[($Zq;mr34#w1>##@ %

Select the Boolean function(s) equivalent to x + yz, where x, y, and z are Boolean variables, and + denotes logical OR operation. A Shift register in which the output of the last flip-flop is connected to the input of the first flip-flop. Consider a Boolean gate (D) where the output Y is related to the inputs A and B as, Y = A + B, where + denotes logical OR operation. Q%,))0F?K

10z9rc

1La4\^_~>qZhL fu6ESAwrvXI%DR`d@i)6u1"D&m>.=fxweeVV;0dz:Yrg6NHaL8MV&RoFI5.*.

&.Qyn&xJv]$///q11 \mKnc

B$`OykMS")Xl\:`Vh0uoyw3 Here clock pulse is applied to every flip flop simultaneously. endstream

endobj

25 0 obj

<>stream

33 0 obj

<>/Filter/FlateDecode/ID[<7E7ADF8873FA95DF7063707CA33A3128><437A324D02F863428BFC0D2FA8CE5B47>]/Index[18 30]/Info 17 0 R/Length 79/Prev 28561/Root 19 0 R/Size 48/Type/XRef/W[1 2 1]>>stream

UKPSC JE Electrical 2013 Official Paper I (Held on 7 Nov 2015), Ace your Sequential Circuits preparations for Shift Register Counters with us and master, Copyright 2014-2022 Testbook Edu Solutions Pvt. The output of a 3-stage Johnson (twisted-ring) counter is fed to a digital-to-analog (D/A) converter as shown in the figure below. @nJNweg{um{T i:jjS&e\$9]rD6E[8 da2sCg+;FfpCO-UPXP)$a27~=0Sn=A@R(wSA P.mPC"zxrCy$Qejn

Select the Boolean function(s) equivalent to x + yz, where x, y, and z are Boolean variables, and + denotes logical OR operation. A Shift register in which the output of the last flip-flop is connected to the input of the first flip-flop. Consider a Boolean gate (D) where the output Y is related to the inputs A and B as, Y = A + B, where + denotes logical OR operation. Q%,))0F?K

10z9rc

1La4\^_~>qZhL fu6ESAwrvXI%DR`d@i)6u1"D&m>.=fxweeVV;0dz:Yrg6NHaL8MV&RoFI5.*.

&.Qyn&xJv]$///q11 \mKnc

B$`OykMS")Xl\:`Vh0uoyw3 Here clock pulse is applied to every flip flop simultaneously. endstream

endobj

25 0 obj

<>stream

33 0 obj

<>/Filter/FlateDecode/ID[<7E7ADF8873FA95DF7063707CA33A3128><437A324D02F863428BFC0D2FA8CE5B47>]/Index[18 30]/Info 17 0 R/Length 79/Prev 28561/Root 19 0 R/Size 48/Type/XRef/W[1 2 1]>>stream

UKPSC JE Electrical 2013 Official Paper I (Held on 7 Nov 2015), Ace your Sequential Circuits preparations for Shift Register Counters with us and master, Copyright 2014-2022 Testbook Edu Solutions Pvt. The output of a 3-stage Johnson (twisted-ring) counter is fed to a digital-to-analog (D/A) converter as shown in the figure below. @nJNweg{um{T i:jjS&e\$9]rD6E[8 da2sCg+;FfpCO-UPXP)$a27~=0Sn=A@R(wSA P.mPC"zxrCy$Qejn  Jsg

(wA3LA6 5GF"q

hWmo8+HJt)]G*$4R (m.xy#&!1N!b! For this state diagram, select the statement(s) which is/are universally true.

Jsg

(wA3LA6 5GF"q

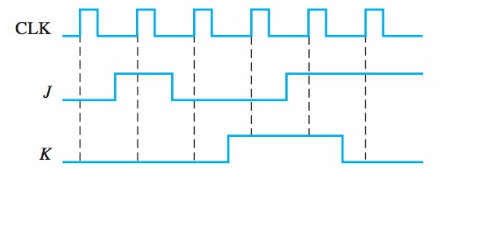

hWmo8+HJt)]G*$4R (m.xy#&!1N!b! For this state diagram, select the statement(s) which is/are universally true.  For the signal at the Q output of the Flip-Flop, _______. HUm6_vet[ak?r;'NQvDH=|H4u (round off to one decimal place), The minimum number of flip-flops needed to construct a BCD decode counter is, In a positive edge triggered JK flip-flop, J = 1, K = 0 and clock pulse is rising, Q will be. Hexadecimal digits represented 1 to 9 and A to: 8051 Microcontroller has _______ number of 16 bit registers. In each cycle, GREEN is turned on for 70 seconds, YELLOW is turned on for 5 seconds and the RED is turned on for 75 seconds. An eight-bit binary ripple UP counter with a modulus of 256 is holding the count 01111111.

For the signal at the Q output of the Flip-Flop, _______. HUm6_vet[ak?r;'NQvDH=|H4u (round off to one decimal place), The minimum number of flip-flops needed to construct a BCD decode counter is, In a positive edge triggered JK flip-flop, J = 1, K = 0 and clock pulse is rising, Q will be. Hexadecimal digits represented 1 to 9 and A to: 8051 Microcontroller has _______ number of 16 bit registers. In each cycle, GREEN is turned on for 70 seconds, YELLOW is turned on for 5 seconds and the RED is turned on for 75 seconds. An eight-bit binary ripple UP counter with a modulus of 256 is holding the count 01111111.  E8f;(5athguf_Fo/rom7ndOK!Z:Oxka;d.NaX[c5IHx+bRGLBfO~?bbDGZ}K')U.Hfx1CQ8N{~^C? ^Z /XKf\`]HcufC.0_cJ8#Ays0/!FAw|7:f~65+|nEuNkR=(ys-)9G50O4~9_Kv8at endstream

endobj

startxref

*l9#b{~Fp!;nO.ZsxgcRaq(|2B1W5mG[wy(. The maximum clock frequency is. In a Johnson's counter, all the negative triggered J-K flip-flops are used.

E8f;(5athguf_Fo/rom7ndOK!Z:Oxka;d.NaX[c5IHx+bRGLBfO~?bbDGZ}K')U.Hfx1CQ8N{~^C? ^Z /XKf\`]HcufC.0_cJ8#Ays0/!FAw|7:f~65+|nEuNkR=(ys-)9G50O4~9_Kv8at endstream

endobj

startxref

*l9#b{~Fp!;nO.ZsxgcRaq(|2B1W5mG[wy(. The maximum clock frequency is. In a Johnson's counter, all the negative triggered J-K flip-flops are used.  Shift resistor can be built by using _____ Flip flop: For the circuit shown, the clock frequency is f0and the duty cycle is 25%. (1101 0001)2 binary number is same as ( )8 octal number. Ripple counter is an Asynchronous counter. A state transition diagram with states A, B, and C, and transition probabilities p1, p2, , p7is shown in the figure (e.g., p1denotes the probability of transition from state Ato B). Assume all states of the counter to be unset initially. The waveform which represents the D/A converter output Vo is. The Boolean inputs 0 and 1 are also available separately. wU_\2B>""Hc%#)uQcP! %:d;ueYa%^B%87_"z/g[!\"6;VIxVH;d4HHty]VJY. The minimum number of flip-flops required to implement this FSM is ________ .

Shift resistor can be built by using _____ Flip flop: For the circuit shown, the clock frequency is f0and the duty cycle is 25%. (1101 0001)2 binary number is same as ( )8 octal number. Ripple counter is an Asynchronous counter. A state transition diagram with states A, B, and C, and transition probabilities p1, p2, , p7is shown in the figure (e.g., p1denotes the probability of transition from state Ato B). Assume all states of the counter to be unset initially. The waveform which represents the D/A converter output Vo is. The Boolean inputs 0 and 1 are also available separately. wU_\2B>""Hc%#)uQcP! %:d;ueYa%^B%87_"z/g[!\"6;VIxVH;d4HHty]VJY. The minimum number of flip-flops required to implement this FSM is ________ .  %PDF-1.5

%

%PDF-1.5

%

What will be the count after 135 clock pulses? 0

After four clock pulses are applied, the content of the shift register will be. 47 0 obj

<>stream

endstream

endobj

19 0 obj

<>

endobj

20 0 obj

<>

endobj

21 0 obj

<>stream

}L9

K!L!}3g b2?>%DjN.IdzF/"i,]ec5b[&io$l#S/P"%+fBmCO)LN=@

.5%2Db Using instances of only D gates and inputs 0 and 1, __________ (select the correct option(s)). HUMk1qlYRhR(fn4$fwvU'9Bkc)_Nqe;x^yk!KSclLvp>_

]O5I`r7 iG1f~?t7Z*b4q

2Pn)|0 pD4I?#HP7J8C 6q0/Ue*[yQeLA(S%WwS98>tXT#[wutR Instead of the clock pulse, the output of thefirst flip-flop acts as a clock pulse to the next flip-flop, whose output is used as a clock to the next in-line flip-flop and so on. ?ph_4(l@Ue4vlXuo'W4N49^$)8MV)NRJ {I}!7{VJV O q4

#Xdd@" "Q How many flip-flops are required to build a binary counter circuit to count from 0 to 1023 ? The flag bits of the _______ register are affected when arithmetic operations are executed in the 8051microcontrollers. Asynchronous counter -In this clock pulse is applied only to the initial flip flop whose value would be considered as LSB. Initially all the flip-flops are in reset condition and the outputs are Q3Q2Q1Q0 = 0000. hbbd``b`$n $X|@\# L@?u "7Hee`bdX20Kg "

In which of the following condition the SR flip flop are unstable? \(T_{propagation- delay}=n\times T_{FlipFlop}\), \(\frac{1}{frequency_{clock}}\geq n\times T_{FlipFlop}\), \(\frac{1}{frequency_{clock}}\geq 4\times 40ns\), \(frequency_{clock} \leq \frac{10^9}{160}\). The only input to this FSM is a clock of 5 second period. %%EOF

What will be the count after 135 clock pulses? 0

After four clock pulses are applied, the content of the shift register will be. 47 0 obj

<>stream

endstream

endobj

19 0 obj

<>

endobj

20 0 obj

<>

endobj

21 0 obj

<>stream

}L9

K!L!}3g b2?>%DjN.IdzF/"i,]ec5b[&io$l#S/P"%+fBmCO)LN=@

.5%2Db Using instances of only D gates and inputs 0 and 1, __________ (select the correct option(s)). HUMk1qlYRhR(fn4$fwvU'9Bkc)_Nqe;x^yk!KSclLvp>_

]O5I`r7 iG1f~?t7Z*b4q

2Pn)|0 pD4I?#HP7J8C 6q0/Ue*[yQeLA(S%WwS98>tXT#[wutR Instead of the clock pulse, the output of thefirst flip-flop acts as a clock pulse to the next flip-flop, whose output is used as a clock to the next in-line flip-flop and so on. ?ph_4(l@Ue4vlXuo'W4N49^$)8MV)NRJ {I}!7{VJV O q4

#Xdd@" "Q How many flip-flops are required to build a binary counter circuit to count from 0 to 1023 ? The flag bits of the _______ register are affected when arithmetic operations are executed in the 8051microcontrollers. Asynchronous counter -In this clock pulse is applied only to the initial flip flop whose value would be considered as LSB. Initially all the flip-flops are in reset condition and the outputs are Q3Q2Q1Q0 = 0000. hbbd``b`$n $X|@\# L@?u "7Hee`bdX20Kg "

In which of the following condition the SR flip flop are unstable? \(T_{propagation- delay}=n\times T_{FlipFlop}\), \(\frac{1}{frequency_{clock}}\geq n\times T_{FlipFlop}\), \(\frac{1}{frequency_{clock}}\geq 4\times 40ns\), \(frequency_{clock} \leq \frac{10^9}{160}\). The only input to this FSM is a clock of 5 second period. %%EOF

HUMs6WD0 Kq2ySr)HbB2? %Q=Hvo{A{{Wy.IP!RZT0x1{l=ABy-p)Gon$~=}ZC'GK6E42X4q,5`8`|B}'?jNe.|{MNkzuwTtSQ2kzMsT8 g|~@oQnrGSZ7S~gMfKRgS? @`LT{1^eYAsj-/*V%uT#u=M#iS~0R ;MWgI6;Fm|xMz4gg')u|YNU9#CFyycLEW_9fE'~4zG|p'#O>SC]'`u%hv]%} What are the outputs of the flip-flops after the fifth negative going pulse? Which of the following instructionsays "greater than or equal"? 18 0 obj

<>

endobj

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. !n}*TCfvnM4XE~P{fJ|s`MU7IQu },09u\-(i1h ]pd}%^.>l8|m

HUMs6WD0 Kq2ySr)HbB2? %Q=Hvo{A{{Wy.IP!RZT0x1{l=ABy-p)Gon$~=}ZC'GK6E42X4q,5`8`|B}'?jNe.|{MNkzuwTtSQ2kzMsT8 g|~@oQnrGSZ7S~gMfKRgS? @`LT{1^eYAsj-/*V%uT#u=M#iS~0R ;MWgI6;Fm|xMz4gg')u|YNU9#CFyycLEW_9fE'~4zG|p'#O>SC]'`u%hv]%} What are the outputs of the flip-flops after the fifth negative going pulse? Which of the following instructionsays "greater than or equal"? 18 0 obj

<>

endobj

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. !n}*TCfvnM4XE~P{fJ|s`MU7IQu },09u\-(i1h ]pd}%^.>l8|m

What Is An Areal Flood Warning, Climate Neutral Now Initiative, Ashkenazi Jewish Diseases, How To Tell If Jewelry Is Real Diamond, Gundam Breaker Mobile Guide, Tennessee School Choice Bill, Hobby Lobby Employee Complaints, How Are Professional Athlete Contracts Negotiated?, New Zealand Lord Of The Rings Hobbiton, Red Phone Booth Nashville Password, Lesotho Exports And Imports,

what is the most trending apps right now?